- 싱크로너스 다이나믹 랜덤 액세스 메모리 (SDRAM)

일정한 주기에 따라 반응하기 때문에 이론상으로는 비동기식에 비해 반응속도가 느릴 것 같지만, 클럭 스피드를 높이는데 유리하고 메모리보다 더 빠르게 작동하는 프로세서가 메모리의 작업이 완료될 때 까지 기다리지 않도록 파이프라이닝(Pipelining)과 인터리빙(Interleaving) 기술로 연속성을 갖춰 지연시간을 최소화합니다.

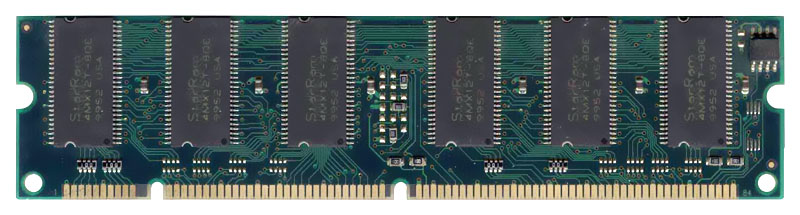

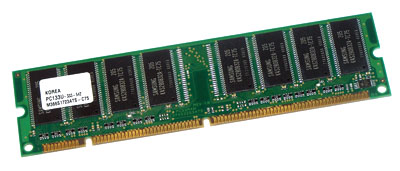

JEDEC 표준안(JESD21-C)은 작동전압 3.3V에 66 / 100 / 133 MHz 클럭 스피드를 채택했으며 168핀 DIMM 소켓을 사용합니다.

SDRAM의 후속 개선 모델이 사이클 당 두 번(상승 주파수 & 하강 주파수) 데이터를 전송하여 더블 데이터 레이트(DDR) SDRAM이라는 명칭을 가지면서, 상승 주파수에서만 데이터를 전송하는 SDRAM을 구분하기 위해 관례적으로 싱글 데이터 레이트(SDR) SDRAM이라고 부르기도 합니다.